依據歐盟施行的個人資料保護法,我們致力於保護您的個人資料並提供您對個人資料的掌握。

按一下「全部接受」,代表您允許我們置放 Cookie 來提升您在本網站上的使用體驗、協助我們分析網站效能和使用狀況,以及讓我們投放相關聯的行銷內容。您可以在下方管理 Cookie 設定。 按一下「全部接受」即代表您同意採用目前的設定。

1-1. 請使用示波器或頻率計測量晶振兩端輸出的訊號。 如果沒有訊號輸出,請依照步驟1-1至步驟1-4執行檢查。 若晶振輸出端(Xout)有訊號輸出,但輸入端(Xin)無訊號輸出,請依照步驟1-5至步驟1-6檢查晶振。

1-2. 請卸下晶振並使用專業測試機測試其頻率和負載電容,看看它們是否振動並符合您的規格。 您也可以將其發送給您的供應商,讓他們為您進行測試。

1-3. 如果出現以下情況,晶振不振動,負載電容與您的規格不符,或者當前頻率與您的目標頻率差距較大,請將晶振寄給您的供應商進行品質分析。 如果頻率和負載電容符合您的規格,我們將需要進行等效電路測試。

1-4. 等效電路測試

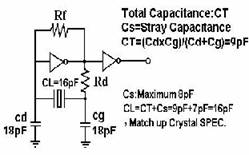

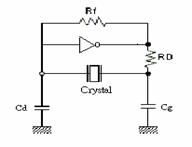

1-4-1. 一般來說,微處理器的振盪電路源自於科爾皮茲電路,如下所示: 圖片1 Cd和Cg是外部負載電容,已內建在晶片組中。 (請參閱晶片組規格) Rf為回授電阻,200KΩ~1MΩ。 它通常是內建在晶片組中。 Rd為限流電阻,阻值為470Ω~1KΩ。 一般電路不需要這個電阻,只有高功率電路才需要這個電阻。

1-4-2. 一個穩定的振盪電路需要負電阻,其阻值至少應為晶振電阻的5倍。 可以寫成|-R| > 5 盧比。 例如,要獲得穩定的振盪電路,當晶振電阻為40Ω時,IC的負阻值必須在–200Ω以下。

1-4-3. 「負阻」是評價振盪電路好壞的標準。 在某些情況下,如老化、熱變化、電壓變化等,如果“Q”值較低,電路可能不會振盪。 因此,請按照以下說明測量負電阻 (-R ) 非常重要:

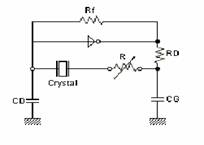

將電阻(R)與晶體串聯 從振盪起始點到終止點調節R的值。 測量振盪期間的 R 值。 您將能夠獲得負電阻值|–R| = R + Rr,Rr = 晶體電阻。 附: 連接電路的雜散電容可能會影響測量值。

1-4-4. 如果晶振參數正常,但在振盪電路中工作不穩定,則需要檢查IC的阻值是否太低,無法驅動電路。 如果是這樣的話,我們可以透過三種方法來改善這種情況: 降低外部電容(Cd和Cg)的值,並採用負載電容(CL)較低的其他晶體。 採用電阻 (Rr) 較低的晶體。 測量振盪期間的 R 值。 採用Cd和Cg不等值的設計。 我們可以增加Cd(Xout)的負載電容,減少Cg(Xin)的負載電容,以提高Xin輸出的波形幅度,用於其後端電路。

1-5. 當Xout有訊號輸出而Xin沒有訊號輸出時,代表後電極後端電路的功耗極大。 我們可以在電路的輸出與其後電極之間添加一個緩衝器來驅動後端電路。

1-6. 除了上述1-1 ~ 1-5的方法外,您還可以按照步驟1-4-4中的三種方法進行操作。 如果無法解決您的問題,請聯絡晶體或IC製造商的現場應用工程師以獲得進一步的協助。

2-1. 請使用示波器或頻率計數器測量晶振兩端的訊號,如果頻率不在規格範圍內且輸出波形幅度不夠(例如超過+/- 200ppm),請依照步驟2-3至步驟 2-5處理。

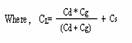

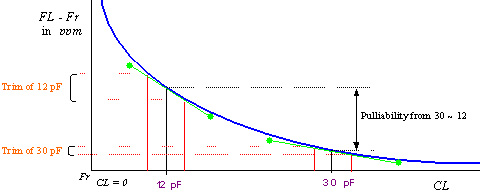

2-2. 電容與頻率的關係公式如下: FL = FR * ( 1 + C1 / 2 * ( C0 + CL) ) 其中 此曲線表示電容變化隨頻率變化的變化(頻率可驅動性):

FL = FR * ( 1 + C1 / 2 * ( C0 + CL) ) 其中 此曲線表示電容變化隨頻率變化的變化(頻率可驅動性):

如果頻率計數器測得的頻率高於目標頻率,則應增加電容值(CL,或Cd&Cg)以將頻率降低至目標頻率,反之亦然。 請檢查調整頻率後波形幅度是否有改善。 如果有所改善,則表示電路的原始設計沒有調諧到晶體的最佳諧振點。 調整諧振點後,晶體應能正常運作。

2-3. 如果頻率非常接近目標頻率但波形幅度沒有改善,我們可以透過以下三種方法來改善:

方法1:降低外部電容(Cd、Cg)值,採用負載電容(CL)較低的晶振。

方法2:採用電阻(Rr)較低的晶振。

方法3:採用Cd、Cg不等值設計。 我們可以增加Cd(Xout)的負載電容,減少Cg(Xin)的負載電容,以提高Xin輸出的波形幅度,用於其後端電路。 建議您採用以上方法,既節省成本又確保安全

2-4. 請使用頻率計數器測量晶振,以確保波形振幅改善後調整後的頻率仍符合原始規格。 如果頻率不符合規格,請根據您的目標頻率採用合適 CL 值的晶振。

2-5. 如果頻率遠高於目標頻率,請採用較低 CL 的晶體,反之亦然。

3-1. 針對頻率輸出偏差超限的問題,可以透過以下方法來改善:

方法1: 調整外部電容 Cd 和 Cg 的值。 如果頻率計數器測量的頻率高於目標頻率,我們應該增加外部電容CL(或Cd和Cg的值),以將頻率降低到我們的目標頻率,反之亦然。

方法2: 採用不同電容(CL)值的晶體。 如果頻率遠高於目標頻率,則採用電容較小的晶體,反之亦然。

3-2. 請在採用正確的電容並將頻率調整到目標值後,使用示波器檢查波形振幅是否正常。 當外接電容導致波形幅度縮小的情況下,請採用方法2調整頻率(減少外接電容,採用電容值較小的晶振)。

4-1. 下面的曲線代表了晶體的電阻特性:

晶體有多種振動模式,如基波、三階泛音、五階泛音…等。當採用基波模式時,晶體的電阻最低,這意味著晶體最容易振盪。 當採用第三音模式時,必須利用放大電路將基模的頻率回授降低到小於第三音模式的程度。 因此,如果頻率僅為目標頻率的三分之一,則應檢查是否使用了放大電路或其設定值是否足夠,因為電路環境適合基頻模式而不是第三音模式。

4-2. 如果不使用放大電路或放大電路設定值不夠,電路可能不會振盪。

4-3. 基本模式與第三音模式的應用如下:

a. 基本模式的應用

b. 第三音模式的應用

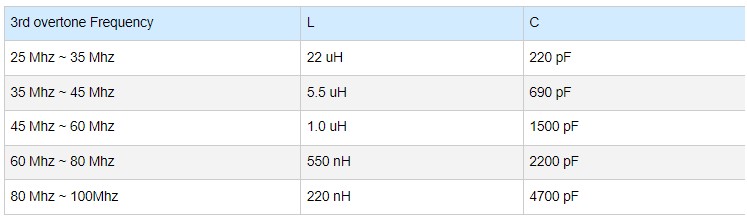

4-4. 下表為Third-Tone模式下不同頻率下L、C的匹配值:

5-1. 這個問題出現的機率比較小。 請判斷三音模態的頻率回授是否因放大電路的原因而大於基模模態的回授。 當放大電路內建於晶片組時,可能會出現此問題。 為了解決這個問題,請採用第三音模式晶振。

5-2. 此外,三音模式放大電路設計不當,也可能導致電路以五音模式振盪或不振盪。

7-1. 請使用頻譜分析儀識別中斷訊號的頻率。 我們可以根據出現的頻率來找出問題所在。

7-2. 如果是電源交流訊號,請檢查電源接地和訊號接地是否懸空。 如果不是請改為浮動。

7-3. 若訊號頻率較高,請採用以下方法: 使用水晶外殼作為接地。 採用C0較小的晶體。 增加電路外部電容Cd和Cg,並採用負載電容CL更高的晶振。

7-4. 如果上述方法無法解決您的問題,請檢查週邊電路和PCB佈局。 如果兩者都正常,請要求IC製造商調查其晶片組設計對未知訊號的反應。 改變週邊電路的設計只能緩解問題,而無法完全解決問題。 通常。 找出晶片組設計的問題並解決它是最好的。

9-1. 請使用示波器或頻率計測量晶體兩端的訊號。 請依照步驟9-1至9-4進行測試。 當Xin有訊號輸出但波形幅度較小時,請依步驟2-1~2-5進行測試。

9-2. 請卸下晶振並使用專業測試機測試其頻率和負載電容,看看它們是否振動並符合您的規格。 您也可以將其發送給您的供應商,讓他們為您進行測試。

9-3. 如果出現以下任何一種情況,例如晶振不振動、負載電容與您的規格不符、或當前頻率與您的目標頻率差距過大,請將晶振寄給您的供應商進行品質分析。

9-4. 如果頻率和負載電容滿足您的規格並且晶體通過DLD測試,我們將需要進行等效電路測試。 請參考步驟1-4~1-6。

9-5. 如果晶體未通過 DLD 測試,請將其發送給您的供應商進行品質分析以進一步改進。

10-1. 拆下晶體並使用熱測試機測試其頻率和電阻,看看是否有振盪並符合規格。 您也可以將其發送給晶振供應商進行測試。 (熱測試點間隔至少10℃/1個測試點)

10-2. 如果晶振在工作溫度下的電阻和頻率超出規格,請將晶振送至製造商進行品質分析並進一步改進。

10-3. 在晶振通過熱測試的情況下,請檢查振盪電路和其他元件的特性(如外部電容的溫度特性、晶片電路的溫度特性等。)。

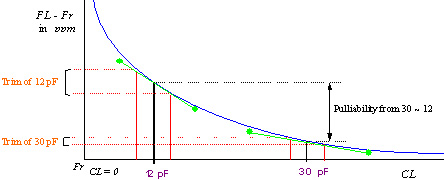

11-1. 如下圖所示,VCXO電路的電容與驅動能力呈負相關,即電容越小,頻率牽引範圍(FL-Fr)越大,反之亦然。 /由於VCXO電路的電容是由壓敏電阻控制的,所以我們可以使用電容值較小的壓敏電阻或調節範圍較寬的壓敏電阻來擴大頻率驅動範圍。

11-2. 除了外部電路調整外,晶體參數的特性也會影響頻率驅動範圍。 其參考參數有Trim Sensitivity(TS)、C0/C1(r)、C1、C0等。各參數與頻率驅動力的關係如下: C0↑ , C1↑, C0/C1(r)↓ , TS↑ , 驅動力 ↑

11-3. 如果頻率驅動範圍不夠,我們還可以調整晶體的規格以滿足目標範圍。

11-4. 當由於驅動範圍不對稱而導致一側驅動力不夠而另一側驅動力太大時,我們可以調整晶振的負載電容(CL),使其達到對稱且兩側驅動力足夠。